令和5年11月27日

各 位

(一社) 電子情報技術産業協会 半導体信頼性技術委員会 WLR/SER PG

## 半導体デバイス信頼性セミナー

# Foundry 活用時代に必要な半導体信頼性の知識とは?

拝啓 時下益々ご清祥のこととお慶び申し上げます。平素は、当協会の諸事業に対しまして格別のご 高配を賜わり、厚く御礼申し上げます。

現在の半導体デバイスの開発・設計・製造業務は広く分業化が進んでおり、特に先端技術を含む CMOS プロセスの場合には、シリコン Foundry を活用する機会が増えています。Foundry を利用した半導体デバイスの開発にあたっては、Foundry から提示されるデータで信頼性検討を行わなければなりません。

一方で、微細化が進む先端 CMOS プロセスでは、世代毎にトランジスタとゲート酸化膜そして、多層配線の摩耗故障の故障メカズムとその信頼性は複雑になっており、その故障メカニズムの内容、試験方法そして寿命推定手順は難解になっています。また、材料中のα線や宇宙線起因で発生するソフトエラーについても同様で、その解釈は難解な項目の一つになっています。

本セミナーでは半導体デバイス信頼性の専門家である JEITA 委員が、半導体 CMOS デバイスの摩 耗およびソフトエラーの故障メカニズムとその信頼性の考え方について、半導体初心者の方にも理解 して頂けるよう丁寧に説明します。また Foundry を使う上での注意点も解説いたします。セミナー内 ではセッションごとに直接講師陣へ質問できる Q&A タイムを設定いたしますので、本項目に知識を 深めたい方、勉強されたい方には最適な内容となっております。ぜひこの機会にご参加いただけます ようご検討ください。

敬具

### 【開催概要】

日 時: 令和6年2月1日(木) 9:30~17:20 (開場9:00~)

場 所: (公財)総評会館 連合会館 402 会議室

〒101-0062 東京都千代田区神田駿河台 3-2-11 (案内図参照)

主 催 : (一社)電子情報技術産業協会 半導体信頼性技術委員会 WLR/SER PG

定 員: 40名(定員になりしだい締め切らせていただきます。)

参 加 費 : 会員 20,000円(税込)

非会員(一般)25,000 円(税込)学生3,000 円(税込)特別参加33,000 円(税込)

<特別参加について>

聴講は2名まで可能です。

また、JEITA 規格(EDR-4705B、EDR-4707A)を1セットお付けします。

※会員・非会員の区分は、下記にてご確認ください。

https://www.jeita.or.jp/cgi-bin/member/list.cgi

※支払方法について

お申込みいただいた方に「電子請求書 (PDF版)」を E-mail でお送りします。 参加費は、セミナー開催前に、事前支払いをお願いしております。 お振込み頂いた参加費は、返金できませんので予めご了承ください。

申込方法: 事前申込制です。下記サイトからお申し込みください。

https://www.jeita.or.jp/form/custom/306/form

申込期限 : 令和6年1月25日(木)

※申込期限までに定員に達した場合は、その時点で締め切らせていただきます。

お申込み後のキャンセルはご遠慮ください。

備 考: セミナーで解説する内容をまとめた資料につきましては、当日配布いたします。

# ■JEITA 規格の特別頒布について

半導体信頼性技術委員会で発行する下記の規格を、本セミナーの参加者限定価格で販売いたします。 この機会にぜひお求めください。

※購入申込書は、セミナー参加をお申込みいただいた方に別途お送りいたします。

| 規格・ガイドライン名                 | 規格番号      | 通常頒布価格   | セミナー参加<br>特別頒布価格<br>(税込) |

|----------------------------|-----------|----------|--------------------------|

| ソフトエラー試験ガイドライン             | EDR-4705B | 5,500円   | 4,000円                   |

| LSI の故障メカニズム及び試験方法に関する調査報告 | ED-4707A  | 12,362 円 | 9,000円                   |

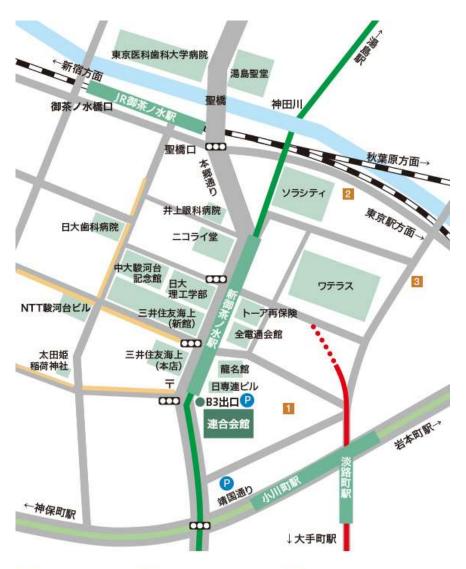

#### ■連合会館へのアクセス (<a href="https://rengokaikan.jp/access/index.html">https://rengokaikan.jp/access/index.html</a>)

(公財) 総評会館 連合会館 402 会議室 〒101-0062 東京都千代田区神田駿河台 3-2-11

東京メトロ千代田線「新御茶ノ水駅」B3 出口より徒歩 0 分 東京メトロ丸ノ内線「淡路町駅」B3 出口より徒歩 0 分 ※ 都営地下鉄新宿線 「小川町駅」B3 出口より徒歩 0 分 ※ ※丸ノ内線、新宿線をご利用の方は地下道を通り、千代田線方面へ

🚺 ザ・ビー お茶の水 🙎 お茶の水ホテルジュラク 💈 ホテルマイステイズ御茶ノ水

**バーキングメーター** (2) 有料駐車場

### プログラム:

| 時間                | タイトル                                                                                                         | 登壇者                                              |  |

|-------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|

| 9:30<br>~<br>9:45 | 開会のあいさつ                                                                                                      | JEITA 半導体信頼性技術委員会 主査<br>宮川 高志 [ルネサスエレクトロニクス (株)] |  |

|                   | 概要説明                                                                                                         |                                                  |  |

| 9:45<br>~<br>9:55 | JEITA WLR/SER PG                                                                                             | ・ 主査<br>茂野 洋一[ルネサスエレクトロニクス(株)]                   |  |

|                   | 本セミナーにて取り上げている故障メカニズムの説明に入る前に、半導体デバイスの生涯使用期間(lifetime)における摩耗故障と偶発故障の位置づけを説明し、各項目がどの段階で発生を想定しているかの内容を説明いたします。 |                                                  |  |

### プログラム:

| <u>/ ロクラム</u>          | •                                                                                                 |                                 |                                                                     |  |

|------------------------|---------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------|--|

| 時間                     | タイトル                                                                                              |                                 | 登壇者                                                                 |  |

|                        |                                                                                                   | デバイスの信頼性<br>Metal gate/FinFET の | D基礎                                                                 |  |

| 9:55<br>~<br>10:30     | JEITA WLR/SER PG 主査<br>茂野 洋一 [ルネサスエレクトロニクス(株)]                                                    |                                 |                                                                     |  |

|                        | シリコン-Fuoudry の先端デバイスに採用されている High-K/Metal Gate や 新規<br>構造のデバイス(FinFET, GAA)について、採用された背景と特徴を説明します。 |                                 |                                                                     |  |

| 10:30<br>~ 休憩<br>10:35 |                                                                                                   | 休憩                              |                                                                     |  |

|                        |                                                                                                   | バイスの信頼性<br>縁膜の経時絶縁破壊            | (TDDB)                                                              |  |

| 10:35<br>~<br>11:30    | JEITA                                                                                             | WLR/SER PG<br>大日方 浩二            | [ソニーセミコンダクターソリューションズ (株)]                                           |  |

|                        | 障メカニ                                                                                              |                                 | 「)のゲート絶縁破壊現象(TDDB)について、その故<br>『方法、そして寿命推定方法を説明し、シリコン・<br>『を解説いたします。 |  |

|                     |                                                                                            | デバイスの信頼性                                                                                                                  |

|---------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|                     | バイアス                                                                                       | K温度不安定性(BTI)                                                                                                              |

| 11:30               | JEITA                                                                                      | WLR/SER PG                                                                                                                |

| ~                   |                                                                                            | 足立 耕作 [ローム(株)]                                                                                                            |

| 12:00               | 変動現象<br>を、近年                                                                               | バイスに使用される MOS 電界効果トランジスタ(FET)の BTI による特性について、その故障メカニズムの説明、評価方法そして寿命推定の方法主流となっている加速モデル含めて説明し、シリコン-Foundry を使用する意点を解説いたします。 |

|                     | <b>:</b> 00                                                                                | お昼休み                                                                                                                      |

|                     | :50                                                                                        | の単体の                                                                                                                      |

|                     | 1                                                                                          | デバイスの信頼性<br>Fャリア注入(Hot Carrier Injection)                                                                                 |

| 12:50<br>~<br>13:35 | JEITA                                                                                      | WLR/SER PG<br>小松原 弘毅 [ラピスセミコンダクタ(株)]                                                                                      |

|                     | 半導体 CMOS デバイスのホットキャリア注入(HCI)による特性変動現象に対し、その故障メカニズムと評価・寿命推定の方法を、近年主流となっている加速モデルも含めて説明いたします。 |                                                                                                                           |

|                     | 半導体デバイスの信頼性<br>配線の断線故障 エレクトロマイグレーション (EM)                                                  |                                                                                                                           |

| 13:35<br>~<br>14:10 | JEITA                                                                                      | WLR/SER PG 主査<br>茂野 洋一[ルネサスエレクトロニクス(株)]                                                                                   |

|                     |                                                                                            | 流を流すことによって発生する断線故障: エレクトロマイグレーション<br>いて、その信頼性の評価方法と最近の問題点、改善策を説明します。                                                      |

|                     | : 10<br>~<br>: 20                                                                          | 休憩                                                                                                                        |

|                  | 半導体デバイスの信頼性<br>配線の断線故障 ストレスマイグレーション (SM)                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 14:20 ~<br>14:55 | JEITA WLR/SER PG<br>松山 英也 [メガチップス(株)]                                                                                              |

|                  | SM は EM と並び半導体デバイスの多層配線の代表的な故障現象です。加速方法が難しくメカニズムに基づいた試験パターンの作成が必要になります。初心者の方にもわかるように基本から説明します。またシリコン-Foundry を使用する上での注意点も補足説明致します。 |

|                  | 半導体デバイスの信頼性<br>Low-k 膜を含む多層絶縁膜(ILD/IMD)の信頼性                                                                                        |

| 14:55<br>~       | JEITA WLR/SER PG<br>土肥 靖弘 [東芝デバイス&ストレージ(株)]                                                                                        |

| 15:30            | 多層配線で発生する TDDB について、故障メカニズム、試験内容、評価パターン、加速モデルについて説明します。また、シリコン-Foundry を活用する際の注意すべきポイントについても説明します。                                 |

| _                | : 30<br><b>一</b> 休憩<br>: 40                                                                                                        |

|                  | 半導体デバイスのソフトエラー<br>α線によるソフトエラー                                                                                                      |

| 15:40 ~          | JEITA WLR/SER PG<br>上薗 巧 [(株) 日立製作所]                                                                                               |

| 16:05            | 半導体デバイスで起こるソフトエラーについて基礎的な説明を行います。その後、<br>代表的な発生原因であるアルファ線の特徴とエラー発生メカニズムおよび評価方法<br>について説明致します。                                      |

|                     |                                      | デバイスのソフトエラー<br>駅によるソフトエラー                                                                   |  |

|---------------------|--------------------------------------|---------------------------------------------------------------------------------------------|--|

| 16:05<br>~<br>16:35 | JEITA WLR/SER PG<br>上薗 巧 [(株) 日立製作所] |                                                                                             |  |

|                     | ーメカニ                                 | ラーのもう一つの発生原因である中性子線について、その特徴と発生エラ<br>ズムに加え、加速器施設を利用した評価方法や近年のエラー率トレンドに<br>明致します。            |  |

|                     |                                      | デバイスのソフトエラー<br>シートの算出とディレーティングの考え方                                                          |  |

| 16:35<br>~<br>17:05 | JEITA                                | WLR/SER PG<br>加藤 貴志[株式会社ソシオネクスト]                                                            |  |

|                     | 続動作試                                 | ラーによる半導体デバイスの故障率(ソフトエラーレート)の算出には、連<br>験から求める場合とは異なるディレーティングの考え方が適用することが<br>。この内容について説明致します。 |  |

|                     | : 05                                 | 質疑応答                                                                                        |  |

| 17                  | : 15<br>: 15<br>~                    | 閉会のご挨拶                                                                                      |  |

| 17:20               |                                      |                                                                                             |  |

※時間および内容の詳細に関しては、予告なく変更する場合がございます。予めご了承ください。

#### ■運営事務局・各種お問合せ先

一般社団法人 電子情報技術産業協会 事業推進戦略本部 事業推進部 担当:岩渕・遠山 〒100-0004 東京都千代田区大手町1丁目1番3号 (大手センタービル)

E-mail : <u>device3@jeita.or.jp</u>

#### ■個人情報保護について

- ※ご参加いただきました方の個人情報は、本セミナーの受付、JEITA主催セミナーのご案内、セミナーアンケートでの質疑回答のために使用いたします。これら以外の目的で使用することはございません。

- ※JEITA の個人情報保護方針につきましては下記をご参照ください。

http://www.jeita.or.jp/japanese/privacy/